内存条如何存储数据靠的是什么材料?

时间:2026-04-06 | 作者:318050 | 阅读:0内存如何存储数据?

内存条依靠硅基半导体材料制成的DRAM芯片存储数据。其核心单元由一个晶体管与一个微小电容构成,即1T1C结构。

电容通过充放电状态分别对应二进制“1”和“0”,晶体管则负责控制读写通断。

这种设计在单位面积内实现了高密度集成,使单根DDR5内存条可容纳64GB甚至更高容量。得益于CMOS工艺的成熟,电容尺寸已缩小至纳米量级。

但其固有漏电特性决定了数据必须每64毫秒刷新一次,这也是“动态”存储之名的由来。

DRAM不依赖磁性、光学或相变等物理机制,纯粹以电荷的瞬时存在为信息载体,在通电状态下实现纳秒级随机访问。这正是CPU得以高效调度海量临时数据的技术根基。

一、物理基础:高纯度单晶硅基底

现代DRAM颗粒全部建立在“九个九”(99.9999999%)纯度的单晶硅晶圆之上。

通过光刻、离子注入与化学气相沉积等一系列精密半导体工艺,才能在硅片上精确构建出数以百亿计的1T1C存储单元。

关键点在于:每个电容并非传统金属极板结构,而是采用了“堆叠式”或“沟槽式”的深亚微米设计。

- 堆叠式:在硅片表面垂直堆叠多层介电材料。 沟槽式:在硅基体内蚀刻出深沟槽再填充导电材料。

这种结构成功将电容体积压缩至0.01平方微米以内,同时还能维持约20飞法的稳定电荷容量。

这意味着,在DDR5标准的1.1V工作电压下,单个电容只要充进去大约两万个电子,就能可靠地区分出代表“1”和“0”的两种电荷状态。

二、维持机制:内存控制器的精密调度

尽管电容存在漏电是固有缺陷,但数据维持并非“被动保持”,其背后是一套由CPU内部内存控制器主导的主动管理系统。

这套控制器严格遵循JEDEC标准,将内存条精细划分为多个bank组,每个bank内部又是行与列的阵列结构。

其刷新机制主要分为两种模式:

- 自刷新模式:系统空闲时,控制器以64毫秒为固定周期,逐行激活各个bank,对所有充电电容进行电荷补充。 自动刷新模式:读写操作活跃期,巧妙利用行地址选通的信号间隙插入刷新动作,整个过程无需CPU额外干预。

实际测试数据佐证了其可靠性。主流DDR5内存在高达85℃的严苛环境下,刷新间隔误差依然能控制在±2%以内,确保了数据安全。

三、断电失忆:由电荷物理特性决定

这与依靠浮栅晶体管长期捕获电子的NAND闪存有根本区别。DRAM的电容天生不具备锁住电荷的能力。

供电一旦切断,电容两端的电压就会迅速衰减,典型的放电时间常数只有几十毫秒。

有第三方实验室用示波器监测DDR4颗粒的断电瞬间,可以清晰看到,电容电压在32毫秒内就跌落到了识别阈值以下。此时读取电路已完全无法判断其逻辑状态。

因此,所有DRAM内存都不支持非易失性存储。这种“临时性”是由材料物理特性和基础电路原理共同决定的刚性约束。

总而言之,内存条的数据存储能力,本质上是:

- 硅材料的电学特性

- 纳米级的工艺精度

- 实时控制算法

三者精密协同的成果。

来源:整理自互联网

免责声明:文中图文均来自网络,如有侵权请联系删除,心愿游戏发布此文仅为传递信息,不代表心愿游戏认同其观点或证实其描述。

相关文章

更多-

- 百度翻译如何翻译菜谱

- 时间:2026-04-09

-

- 懂车帝怎么看文章

- 时间:2026-04-09

-

- 企鹅FM音效怎么设置

- 时间:2026-04-09

-

- 铁路12306如何在线办理退票

- 时间:2026-04-09

-

- 醒图如何修改比例

- 时间:2026-04-09

-

- 3dmax2009如何制作时钟

- 时间:2026-04-09

-

- 国家超算互联网平台官网入口在哪

- 时间:2026-04-09

-

- 怎么查看候补车票排位

- 时间:2026-04-09

精选合集

更多大家都在玩

大家都在看

更多-

- DNF2026魔道技能数据大核心要点全凸显

- 时间:2026-04-12

-

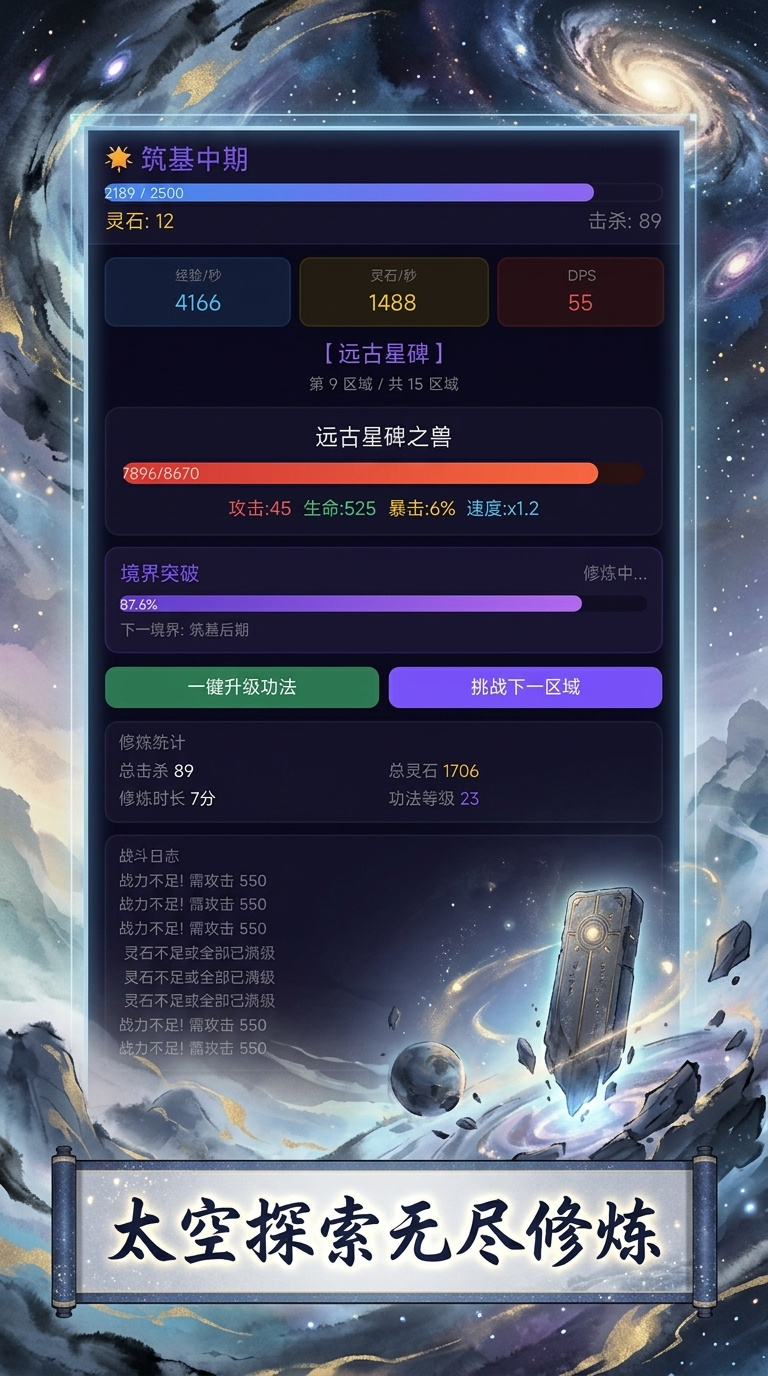

- 太空修仙录什么时候出 公测上线时间预告

- 时间:2026-04-12

-

- 战地6NVO288E好用配件搭配推荐

- 时间:2026-04-12

-

- 惊爆 烈火星辰传奇技能大,超强玩法等你体验,速来一探究竟

- 时间:2026-04-12

-

- 燕云十六声众生宝箱介绍 全面解析与探秘

- 时间:2026-04-12

-

- 地下城手游迷你商店换什么装备 地下城手游迷你商店的装备选择建议是什么

- 时间:2026-04-12

-

- 绝地求生中眼泪一两声是什么意思 怎么在游戏中触发

- 时间:2026-04-12

-

- 迅雷光鸭云盘开启公测招募:不限速、免登录 2TB免费空间

- 时间:2026-04-12