死磕Intel!台积电3大技术路线公布:1.6nm明年见、1.4nm坐火箭

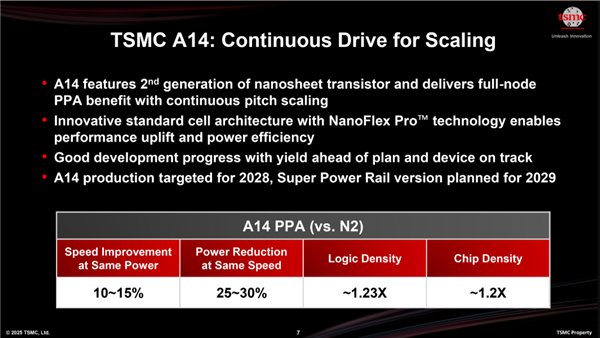

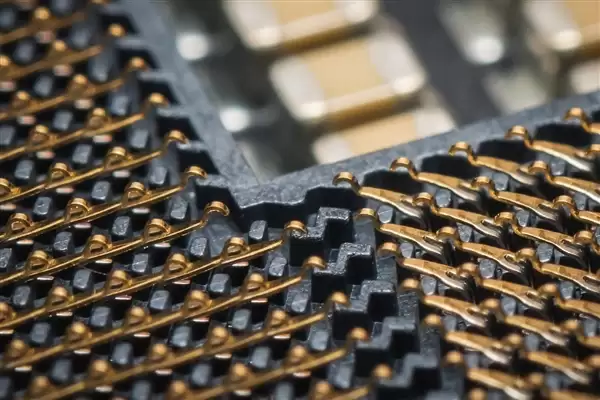

时间:2025-05-04 | 作者: | 阅读:05月4日消息,上个月,台积电在北美技术研讨会上发布了其最先进的A14工艺(1.4nm级),从命名到技术直接对标Intel 14A,后者同样号称1.4nm级工艺。

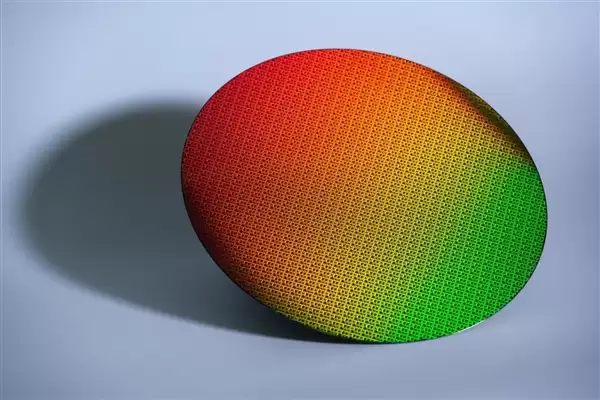

台积电承诺该技术将在性能、功耗和晶体管密度方面,相较于其N2(2nm级)工艺带来显著提升。

台积电声称,A14计划于2028年投产,目前开发进展顺利,良率已提前实现。ps. Intel 14A预计都将在2027年投入风险性试产,顺利的话2028年就能量产。

随后,Tom's Hardware专访了台积电业务开发资深副总裁张晓强,后者详细分享了台积电的3大技术路线。

据了解,台积电将提供不同领先制程技术,再根据各细分市场进行客制化,成为“所有人的晶圆代工厂”(Everyone's Foundry)。

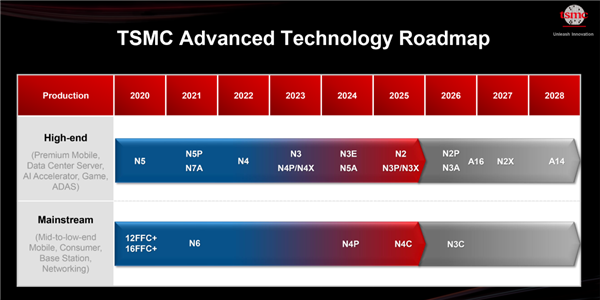

换而言之,为了满足不同市场需求,台积电将提供多种领先的制程技术,并围绕三种方向调整其技术路线,分别是——先进的晶体管扩充、电源传输优化,以及多芯片(multi-chiplet)系统整合。

首先是追求最大晶体管密度、最高性能效率。

针对智能手机与PC这类产品,台积电将提供N3P、N2、N2P与A14制程技术,针对“每瓦性能”进行最佳化,同时避免背面供电(backside power delivery)的复杂性与成本,使得移动与消费SoC在面积效率与电池续航间取得最佳平衡。

其次是以合理成本提供最佳电源,实现最高性能效率。

对于功耗一千瓦以上的数据中心处理器,台积电计划2026年底推出配备晶背供电(BSPDN)的A16,随后在2029年推出配备超级电轨技术(Super Power Rail,简称SPR)的A14。

第三是适用数据中心的多芯片封装解决方案

为满足数据中心等级AI基础设施对多芯片封装解决方案需求增加,台积电已扩展其先进封装技术组合,涵盖硅光子与嵌入式电源组件,打造一体化、高带宽、节能的系统方案。

谈到摩尔定律是否已死? 张晓强认为,制程从5nm发展到A14,目前看到的趋势是,每代功耗效率降低约30%,并以每代20%左右的速度提高晶体管密度,效能则提升15%,与过往的进展基本上是一致的。

展望A14以下制程,张晓强表示台积电也有信心延续这个趋势,“从N2到A16的转变相当大,台积电完全有信心在2028年实现A14量产,实现大幅微缩,帮助客户受益于制程技术本身的进步优势。”

A14是台积电的下一代制程技术。台积电称,其表现将明显超越当前最先进的3nm制程,以及今年晚些时候即将量产的2nm制程。

据台积电公布的数据显示,与N2工艺相比,A14将在相同功耗下实现高达15%的速度提升,或在相同速度下降低高达30%的功耗。

展望未来,台积电还计划依次推出A14P、A14X、A14C等多种版本的衍生制程,其中, A14P是包括背侧电力供应在内的高性能版本,A14X和A14C将分别以性能最优化型和成本节省型模式进行优化。

此外,台积电还计划在2026年底推出A16(1.6nm级)制程技术。

来源:https://news.mydrivers.com/1/1045/1045510.htm

免责声明:文中图文均来自网络,如有侵权请联系删除,心愿游戏发布此文仅为传递信息,不代表心愿游戏认同其观点或证实其描述。

相关文章

更多-

- 台积电跃居全球第七大公司:美股市值达1.8万亿美元

- 时间:2026-04-27

-

- 1.3、1.2nm两联发 台积电公布A13A12工艺:2029年问世

- 时间:2026-04-23

-

- 1.3、1.2nm两联发 台积电公布A13、A12工艺:2029年问世

- 时间:2026-04-23

-

- 台积电亮出新一代芯片技术 拟绕开ASML天价设备

- 时间:2026-04-23

-

- 要求熟悉2nm工艺 马斯克芯片工厂要挖台积电高级人才

- 时间:2026-04-18

-

- 台积电三星步步紧逼!成熟晶圆代工集体提价 联电2026下半年跟进约10%涨幅

- 时间:2026-04-17

-

- 不怕成本高 台积电表态:扩大对美国投资 更有信心了

- 时间:2026-04-17

-

- Intel、马斯克杀入2nm 台积电回应竞争:他们也没捷径可走

- 时间:2026-04-16

精选合集

更多大家都在玩

大家都在看

更多-

- 修真高手手游贞德阵容搭配指南

- 时间:2026-05-02

-

- 红色沙漠战场之光套装怎么获得

- 时间:2026-05-02

-

- 红色沙漠残响峭壁古代遗迹解谜攻略

- 时间:2026-05-02

-

- 龙魂大陆戒指如何获取-龙魂大陆怎么得到戒指

- 时间:2026-05-02

-

- 牧场气息手游精灵玩法指南

- 时间:2026-05-02

-

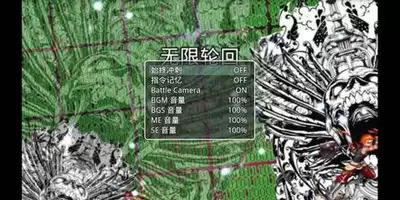

- 无限轮回推图的方法是什么-无限轮回如何进行推图

- 时间:2026-05-02

-

- 落落大方的你配上自拍照朋友圈就这么发

- 时间:2026-05-02

-

- 适合五月发的朋友圈文案

- 时间:2026-05-02