芯片工艺发展前景乐观未来二十年将持续突破至零点二纳米以下

时间:2026-05-09 | 作者:318050 | 阅读:0不用悲观 芯片工艺还能再战20年:2046年直奔0.2nm以下

摩尔定律引领全球芯片工艺发展已超过半个世纪。最近十几年,“摩尔定律已死”的论调不绝于耳。

许多人认为芯片工艺即将触及物理极限,微缩之路难以为继。

然而,比利时的欧洲微电子中心IMEC却给出了不同的展望。他们最新公布的路线图显示,硅基工艺的生命力远比想象中顽强。

至少在未来二十多年里,仍有清晰的发展路径。路线图甚至规划在2046年实现0.2纳米以下的工艺节点。

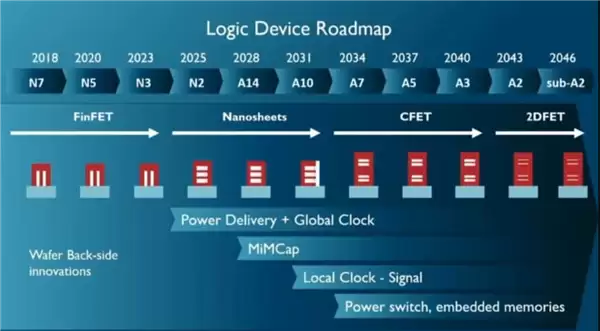

技术路线演进:从FinFET到2DFET

根据这份路线图,产业界在2018年实现了7纳米级别的N7工艺。从那时起,直到3纳米的N3工艺,都依靠FinFET晶体管结构支撑。

转折点出现在去年。2纳米节点的N2工艺开始转向GAA晶体管,具体采用的是NanoSheets技术路线。

这种结构预计将沿用至1.4纳米的A14及1.0纳米的A10工艺,时间窗口大约持续到2031年。

2034年后的变革:CFET登场

真正的变革将在2034年前后到来。届时,产业有望进入0.7纳米级别的A7工艺。

到了这个尺度,现有的GAA晶体管结构也将面临挑战,取而代之的将是CFET,即互补场效应晶体管。

这种结构通过将N型和P型晶体管垂直堆叠,理论上能将芯片面积缩减一半。当然,其带来的散热挑战也堪称巨大。

CFET晶体管结构预计将支撑工艺演进至2040年的0.3纳米A3节点。

终极展望:二维材料时代

再往后呢?路线图指向了传闻已久的2DFET——这意味着芯片工艺将进入二维晶体时代。

二维材料被视为芯片制造的终极材料之一,其完美的原子级厚度特性令人神往。

台积电、三星、英特尔等行业巨头都曾展示过相关技术,但距离大规模量产,目前仍无明确时间表。

如果2DFET晶体管成为现实,芯片工艺将有望一路推进至Sub-A2,即0.2纳米以下。按照现行命名规律,那可能就是0.14纳米级别了。

不过,谈论具体的命名还为时尚早,毕竟那是二十年后的事情。IMEC此刻给出的更多是一个前瞻性的技术愿景。

埃米级工艺的挑战

总而言之,IMEC为我们勾勒出了一幅直至2046年的芯片工艺发展蓝图。但必须清醒认识到,一旦进入埃米级(亚纳米)工艺,每一代技术的提升都将变得异常艰难。

如果你关注过台积电2纳米之后的工艺规划,就会发现芯片面积的微缩已不再像过去那样显著。密度提升哪怕10%都极为困难。

这正是为什么近期出现了许多“非标准”的工艺代际命名。例如前不久技术论坛上公布的A13、A12工艺,它们就是为了填补A14到A10之间的空白。未来即便出现A11工艺,恐怕也不会让人感到意外。

此外,评判芯片工艺的先进性,早已不能单纯看纳米数字的大小。以下几个关键领域的挑战同样至关重要,甚至可能成为决定性因素:

- 散热

- 供电

- 封装集成

谁能在这几个关键领域取得突破,谁就有机会在未来二十年的工艺竞赛中脱颖而出,实现对台积电、三星或英特尔等现有领先者的超越。

期待更多参与者

展望未来二十年的竞争格局,我们期待看到更多参与者。

希望中芯国际、华虹、晶合集成、芯联集成等中国大陆的企业能够深度融入这场技术长征,不再仅仅是追赶者,而是成为重要的创新力量之一。

来源:整理自互联网

免责声明:文中图文均来自网络,如有侵权请联系删除,心愿游戏发布此文仅为传递信息,不代表心愿游戏认同其观点或证实其描述。

相关文章

更多-

- 总投资高达1190亿美元!马斯克拟在美国得州建设半导体工厂

- 时间:2026-05-08

-

- ASML CEO预警:AI芯片短缺将延续数年 新光刻机虽贵但能降成本

- 时间:2026-05-06

-

- 怪兽盟约芯片词条如何搭配-怪兽盟约芯片词条搭配方法

- 时间:2026-05-05

-

- 马斯克:未来AI芯片将严重不足 不自己造芯片就会遇到瓶颈

- 时间:2026-04-23

-

- 台积电亮出新一代芯片技术 拟绕开ASML天价设备

- 时间:2026-04-23

-

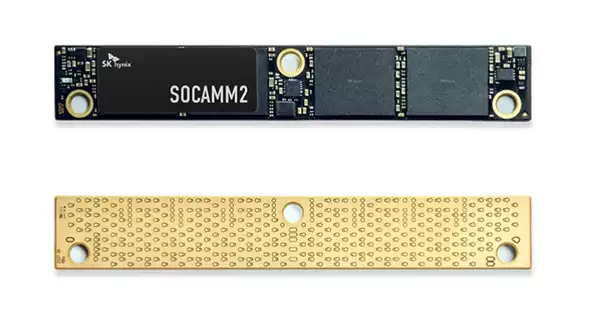

- 1cnm工艺加持!SK海力士量产192GB SOCAMM2内存模组:带宽翻倍能效提升超75%

- 时间:2026-04-20

-

- 不止A20 Pro!iPhone 18 Pro系列还将搭载全新C2、N2芯片

- 时间:2026-04-05

-

- 内存疯涨导致千元机消失!4nm芯片出货量暴跌

- 时间:2026-04-04

精选合集

更多大家都在玩

大家都在看

更多-

- iPhone白噪音开启教程 苹果手机背景声音设置方法

- 时间:2026-05-09

-

- iCloud空间不足照片会丢失吗 满额后注意事项与解决方法

- 时间:2026-05-09

-

- 小米手机内存清理全攻略 彻底清除系统缓存方法详解

- 时间:2026-05-09

-

- 男生霸气网名大全:精选100个,怎么选?为什么酷?

- 时间:2026-05-09

-

- 男生网名大全:100个精选推荐,怎么选?为什么火?

- 时间:2026-05-09

-

- 《幻灵召唤师》午夜挽歌版本重磅来袭

- 时间:2026-05-09

-

- 拼多多小编推荐机制解析如何提升商品入选概率

- 时间:2026-05-09

-

- 男生网名“枫落无痕”好听吗?精选100个推荐

- 时间:2026-05-09